试题二

阅读以下关于某嵌入式处理器和存储器方面的说明,回答下列问题。

[说明]

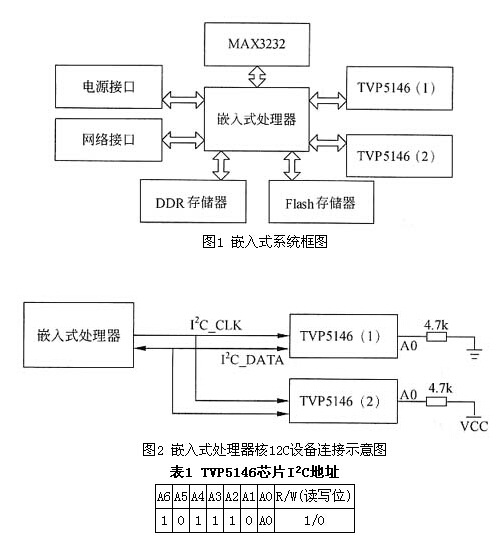

在某嵌入式系统设计中,需要使用嵌入式主处理器对外围模拟视频信号进行采集、编码、存储和网络传输。图1为李工设计的该嵌入式系统的原理框图:采用两片TVP5146芯片进行两路模拟视频数据采集,在该处理器外围采用MAX3232芯片进行串口扩展,以方便系统调试,同时在该原理图中还设计了相应的Flash存储器接口,DDR存储器,网络及电源等电路。

在该电路设计中,视频采集芯片TVP5146需要主处理器通过I2C接口进行采集模式、亮度、对比度、增益等参数的调节,但是主处理器只有一个I2C接口,因此需要将两个TVP5146挂载的同一个I2C总线上,如图2所示TVP5146的I2C芯片地址选择如表1所示,当进行I2C读时,I2C地址的最低位是1,当进行写操作时,I2C地址最低位是0,A0由外围电路的高低电平决定,高电平为1,低电平为0。

(答案用十六进制表示,比如0xAA)

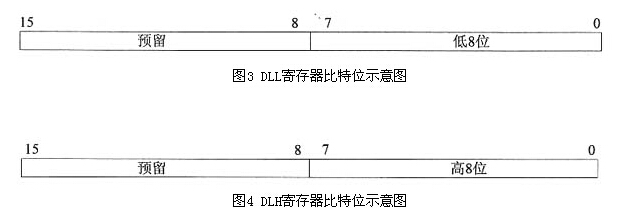

在图2原理图设计中,主处理器的串口控制器的时钟为27M,在进行串口调试时,李工需要将串口配置为9600bps的波特率,需要对串口控制器的DLL(DivisorLatchesLow寄存器)和DLH(DivisorLatchesHigh寄存器)进行配置,DLL和DLH的寄存器分别如图2-3和图2-4所示。

根据以上信息,DLL和DLH寄存器应该分别被配置为:

DLL:____(1)____

DLH:____(2)____

参考答案:

(1)0xFC或者0xFD (2)0x0A

解析:

本题考查嵌入式系统中的硬件驱动配置,要求考生能够正确配置串口的波特率。 在图2原理图设计中,主处理器的串口控制器的时钟为27M,在进行串口调试时,需要将串口配置为9600bps的波特率,需要对串口控制器的DLL(Divisor Latches Low寄存器)和DLH(Divisor Latches High寄存器)进行配置,同时该题目给出了DLL和DLH的寄存器定义。由定义可以看出来,其DLH和DLL分别为16位寄存器,但是只有低8位是有效的。 在该题目中给出了对应的串口控制器的时钟,其波特率配置寄存器DLL和DLH的配置实际就是依据时钟和需要配置的波特率数值进行计算。在实际的嵌入式系统的驱动程序设计中,对于驱动的设计也就是如此。其计算方法为: (1)9600bps的波特率则意味着每个比特位数传输所需要的时间为1/9600秒。 (2)串口控制器的时钟为27M,说明其对应的时钟周期时间为1/(27*1000*1000)秒。 (3)因此,传输每个比特位所需要的时钟周期数目为:(1/9600)/(1/(27*1000*1000))=2812.5。 2815.2换算为十六进制为AFCH或者是AFDH,因此对应的DLH设置为高8位,0x0A,对应的DLL设置为低8位,为0xFC或者0xFD。

,则存在函数u=u(x),使______.

,则存在函数u=u(x),使______.