问题

问答题

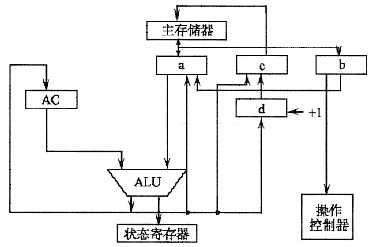

下图是一个简化的CPU与主存连接结构示意图(图中省略了所有多路选择器)。其中有一个累加寄存器AC、一个状态数据寄存器和其他四个寄存器:主存地址寄存器MAR、主存数据寄存器MDR、程序计数器PC和指令寄存器IR,各部件及其之间的连线表示数据通路,箭头表示信息传递方向。

要求:

(1)请写出图中a、b、c、d四个寄存器的名称。

(2)简述图中指令从主存取到控制器的过程。

(3)说明数据从主存取出、运算、写回主存所经过的数据通路(假定数据地址已在MAR中)。

答案

参考答案:(1)a表示的是主存数据寄存器MDR,b表示的是指令寄存器IR,C表示的是主存地址寄存器MAR,d表示的是程序计数器PC。

(2)指令从主存取到控制器的过程可描述为:PC将内容送给主存地址寄存器MAR,然后自加1。在读命令的作用下,主存中MAR所选中的存储单元的内容送给指令寄存器IR。

(3)数据地址寄存器MAR选中存储单元后,在读命令的作用下,主存中MAR所选中的存储单元的内容送给主存数据寄存器MDR,在ALU中完成运算(或另一个操作数送AC后两者运算),运算结果送回MDR,在写命令的作用下,MDR的内容写入到由MAR所选中的存储单元。