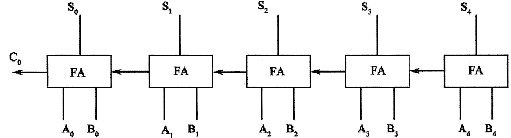

下图给出了一补码加法器,图中A0、B0分别为两个操作数的符号位,A1、B1分别为操作数的最高有效数字位,要求:

(1)增加能实现减法运算的逻辑电路。并说明加、减法是如何被控制实现的。

(2)在给定电路的基础上增加以变形补码进行运算、具有溢出检测功能的逻辑电路。

参考答案:(1)增加能实现减法运算的逻辑电路如下图所示:

当SUB=1时,B的各个位和1进行异或,根据异或的性质,逻辑变量和1异或相当于对逻辑变量取反,即B0B1B2B3B411111=[*] ,且最低位(A4B4)的全加器因为SUB=1,所以加上了一个1,使得:

[*]

此时通过补码加法完成了减法操作。

当SUB=0时,B的各个位和0进行异或,同理根据异或的性质

B0B1B2B3B400000=B0B1B2B3B4

所以,通过全加器A0A1A2A3A4+B0B1B2B3B4+0=A+B,完成了加法操作。

[*]

(2)在给定电路的基础上。增加以变形补码进行运算、具有溢出检测功能的逻辑电路,可在符号位旁增加一个全加器完成双符号位中新符号位相加,并且全加器的输出和原有的符号位的输出进行异或,异或结果如果为1,则表示溢出,反之,则没有溢出。逻辑电路图如下所示:

[*]