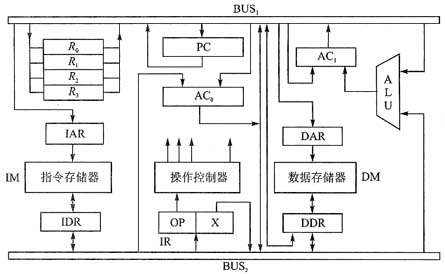

下图所示的CPU逻辑框图中,有两条独立的总线和两个独立的存储器。已知指令存储器IM最大容量为16384字(字长18位),数据存储器DM最大容量是65536字(字长16位)。各寄存器均有“打入”(Rin)“送出”(Rout)控制命令,但图中未标出。

(1)指出下列寄存器的位数:

程序计数器PC,指令寄存器IR,累加器AC0、AC1,通用寄存器R0~R3,指令存储器地址寄存器IAR,指令存储器数据存储器IDR,数据存储器地址寄存器DAR,数据存储器数据寄存器DDR。

(2)设机器指令格式为

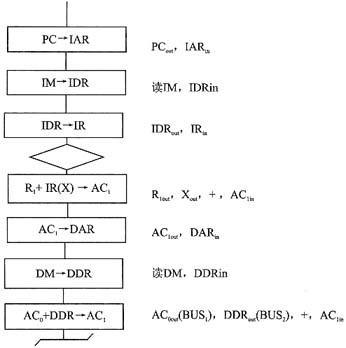

加法指令可写为“ADD X(Ri)”,其功能是(AC0)+((Ri)+X)→AC1,其中((Ri)+X)部分通过寻址方式指向数据存储器DM。现取Ri为R1。画出ADD指令的指令周期流程图,写明“数据通路”和相应的微操作控制信号。

参考答案:[解答] (1)PC=14位,IR=18位

AC0=AC1=16位,R0~R3=16位

IAR=14位,IDR=18位

DAR=16位,DDR=16位

(2)加法指令“ADD X(Ri)”是一条一地址指令,其中一个操作数来自AC0,另一个操作数在DM中,其地址由通用寄存器的内容(Ri)加上指令格式中的X量值决定。其指令周期流程图如下图所示,相应的微程序控制信号标在框图外面。

解析: (1)由于指令存储器IM的容量为16384*18,数据存储器DM的容量为65536*16,可以推出相应寄存器的位数。

(2)根据数据通路,可以写出加法指令的微操作控制信号。

[归纳总结] 在CPU逻辑框图中,有两个独立的存储器.指令存储器存放指令,指令字长18位,数据存储器存放数据,数据字长16位。加法指令“ADD X(Ri)”采用的寻址方式是偏移寻址,通用寄存器R,的内容加上指令格式中的形式地址X形成有效地址.根据此有效地址到数据存储器DM中取出操作数,与累加寄存器AC0的内容相加。