[说明]

通常计算机按其体系结构分为冯·诺依曼(Von Neumann)结构和哈佛(Harvard)结构。冯·诺依曼结构,也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构。哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。复杂系统的不同处理器可采用不同类型体系结构。

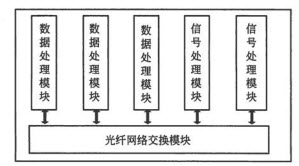

某嵌入式系统由数据处理模块、信号处理模块和光纤网络交换模块组成,如图1-1所示。其中数据处理模块的主处理器选用PPC7447,内部集成了二级Cache,并有SDAM存储器、FLASH、NvRAM、实时时钟、FC(Fabric Channel)通信接口、以太网接口和RS232接口;信号处理模块采用DSP TMS320C6000,并有FC通信接口、RS232接口,用于SPM与外部数据通信;光纤网络交换模块提供FC协议交换能力,主要由控制单元和交换单元两部分组成。

本嵌入式系统的数据处理模块主要接收外部命令、控制系统运行、与系统其他模块通信;信号处理模块主要进行图形图像处理,需要较大的运算量和较高的运算速度。

回答下列问题,将答案填写在对应的栏目中。

在设计数据处理模块DPM时,假设某桥芯片内部集成一路递增定时器,定时器宽为32位,最高为控制使能位,输入时钟为24MHz。请回答下面三个问题,将答案填写在答题纸对应的栏目中(给出表达式即可)。

(1)该定时器最长定时时间是多少(单位ns)?

(2)设置10ms定时时间,则定时器的初值是多少?

(3)若改为一路抵减时间,设置10ms定时时间,则定时器的初始值为多少?

参考答案:

(1)40×231或85899345920

(2)231-10×106/40或2147233648

(3)10×106/40或250000

解析:

计时器位宽为32位,而最高位为控制位,所以用于计数的位宽为31位,计数个数为231,所以最大计时长度为231个时钟周期。在25MHz的时钟周期下,单个时钟周期的长度为40ns,因此计时器的最大计时长度为40×231ns(或85 899 345 920ns)。

在递增计时的情况下,需要从初值开始递增到0x7fffffff结束,10ms的时长需要10×106/40个时钟周期,亦即250000个时钟周期。但由于是从初值开始递增到0x7fffffff,所以定时器的初值应该为最大计数值减去10ms时长对应的计数值,即231-10×106/40或2147233648。

在递减计时的情况下,从0x7fffffff开始进行递减。10ms的时长同样需要10×106/40(或250000)个时钟周期,因此定时器的初值应该设为10×106/40或250000。